PCB设计实战避坑指南:从封装到测试的全流程关键要点

硬件工程师的设计生涯中,调试与改板往往占据大量精力。PCB设计过程中看似微小的决策失误,都可能导致整批电路板报废。本文摒弃高深理论,聚焦封装管理、布局规划、信号处理、制板贴片及测试验证等核心环节,分享经实践验证的实战经验与避坑要点。以下为具体内容。

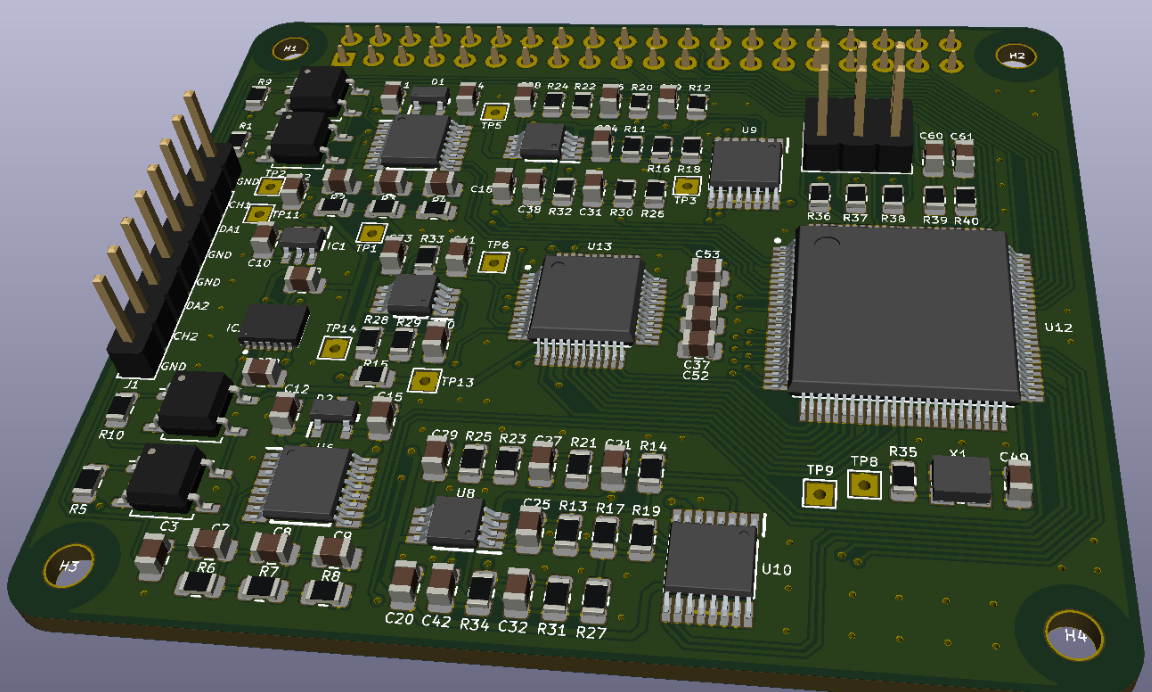

在硬件设计初期,笔者自主绘制原理图与PCB封装时,严格确保引脚一一对应,未出现过封装问题。但在后续入职不同企业后,需接手多类项目及经不同软件转换的设计文件,进行增减改删操作。当多项目并行推进、工期紧张时,若省略封装核验步骤,极易引发封装故障。以下为真实案例带来的启示:

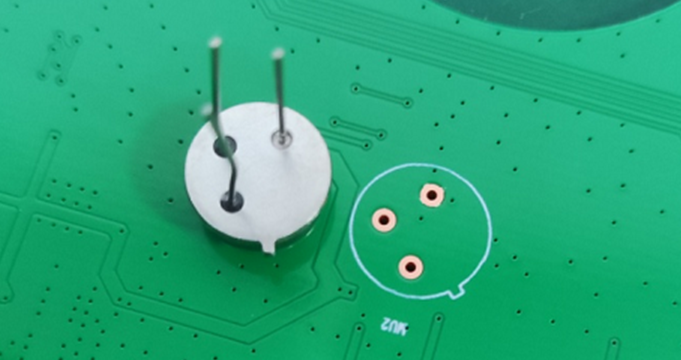

1. 严禁滥用未经验证的封装库:封装的精准性如同紧固件的适配性,设计中所谓的“近似匹配”,实际应用中往往导致器件无法装配。切勿因库内封装名称一致便直接调用,未经规格书核验与实际验证的封装,本质上就是一颗“定时炸弹”。除核心芯片外,按键、USB接口、三极管、排针等各类器件,若采用他人提供的封装,必须逐一核对原理图与PCB封装的引脚定义、排列顺序,确保完全匹配,否则将面临器件装配失败的风险。

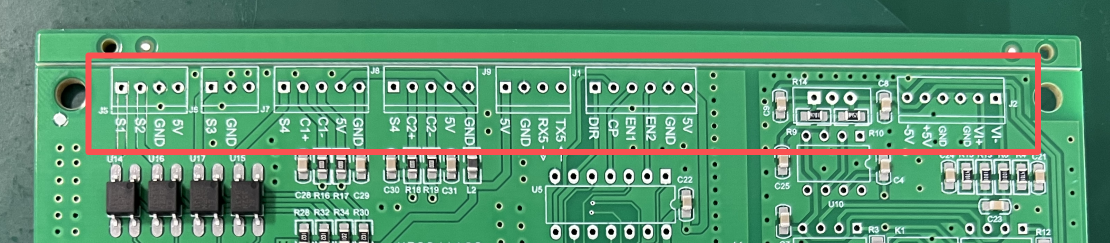

2. 重视丝印设计的完整性:对于立式连接器,仅依靠丝印框难以精准判断安装方向。奇数引脚(如5引脚)可通过引脚数量差异辅助判断,但偶数引脚(如6引脚、8引脚、10引脚等)需通过完善的丝印设计明确方向。建议在丝印框内外均增设标识,外部丝印便于贴片后的外观检测。即便封装本身无误,若丝印设计不完善,仍会在贴片首件检测阶段耗费大量时间确认器件方向。

PCB设计需充分结合结构要求,避免电路板制作完成后才发现装配问题。以下为需重点把控的细节要点:

1. 严守禁布区规范:螺丝孔帽周围1mm范围内属于禁布区,禁止布设导线与器件。曾出现某DIY电路板将电阻贴装于螺丝孔旁,锁紧螺丝时直接压损电阻的案例。经分析,该问题源于设计阶段DXF文件中螺丝帽丝印位于非显示层,导致出GERBER文件时未体现螺丝帽直径,进而被设计人员忽略。建议将螺丝帽丝印设置为显性显示,并采用红色标识以强化警示。此外,螺丝帽覆盖区域内禁止布线,若因PCB空间限制必须布线,需覆盖白油以降低锁紧螺丝时导线受损的概率。

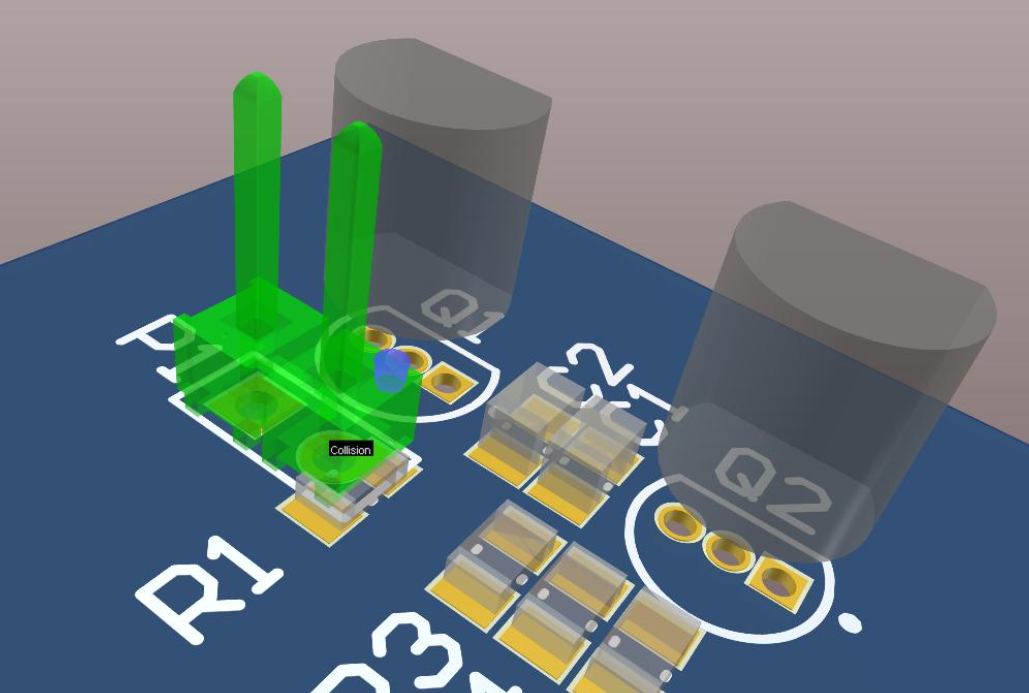

2. 充分利用3D预览进行限高检查:当前主流EDA工具均具备3D预览功能,设计过程中需通过旋转视角,核查电解电容等高度较高的器件是否与外壳发生干涉。若省略该步骤,一旦出现器件顶壳且无替代矮件的情况,将导致设计返工。

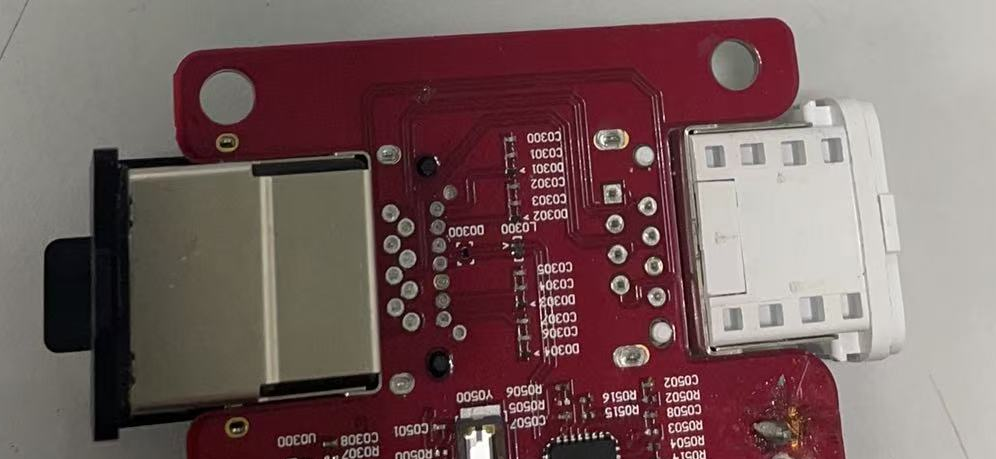

3. 合理规划连接器与板边距离:USB、音频接口等连接器需尽量靠近板边。若连接器与板边距离超过2mm,拼板时需开设足够尺寸的凹槽——尤其部分3.5mm音频接口头部存在下沉设计,若凹槽尺寸不足,会导致贴片时器件翘起,影响焊接质量。USB-C接口因采用直边设计,对凹槽要求较低;而USB-A、Micro-USB等早期带卷边的接口,拼板时需预留符合要求的凹槽。

4. 强制绑定3D模型:某项目中,板上AUX接口因封装引脚反向与外壳干涉,经排查为设计周期紧张导致规格书研读不细致。若提前为器件绑定3D模型,通过EDA工具的3D预览功能,可快速发现插件焊盘与3D模型引脚的错位问题,规避此类风险。

时钟信号毛刺、视频信号纹波等信号完整性(SI)问题,部分难以在原理图阶段预判,但可通过PCB设计进行规避。以下为核心实战要点:

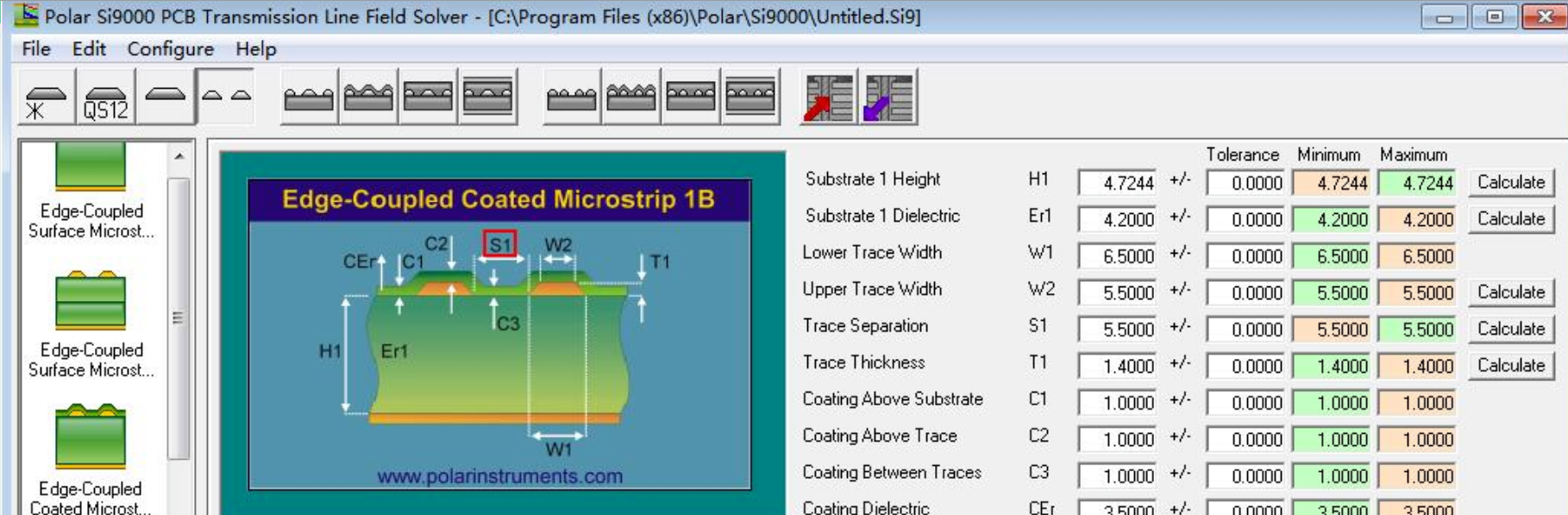

1. 阻抗控制为必选项:50Ω单端阻抗、100Ω差分阻抗为行业通用标准。进行叠层设计时,必须借助Polar SI9000等专业工具进行阻抗仿真,不可仅凭经验判断——即便板厂可通过微调线宽与间距优化阻抗,若初始设计偏差过大,仍无法满足要求。建议参考专业资料,确保阻抗设计精准。

2. 严格执行等长匹配:某PCIe接口电路板在多数PC上正常工作,但在特定型号PC上出现异常。经对比同型号合格电路板发现,合格产品的等长误差控制在3mil以内,而该故障电路板的等长误差达10mil。设计时侥幸认为误差可接受,忽略了PC主板本身的误差,两者叠加导致信号传输异常。建议差分对的等长误差控制在5mil以内,时钟信号组内等长误差不超过10mil,充分利用EDA工具的等长绕线功能。严格的等长设计是通过PCIe、USB4等高速协议眼图与抖动测试的必要条件,直接决定链路传输速率与稳定性。

某项目中,芯片VDD供电引脚共6个,原理图中仅配置3个去耦电容,设计人员称其严格按照规格书绘制。电源设计中,相较于无输出的显性故障,输出噪声异常更具隐蔽性——可能导致模拟电路噪声超标、数字电路随机复位等问题。以下为电源设计的核心心得:

1. 掌握去耦电容的布局技巧:0.1μF陶瓷去耦电容必须紧贴IC电源引脚(间距不超过5mm),确保每个电源引脚均配备独立去耦电容;大容量电解电容可布置在稍远位置,形成“远近搭配”的供电滤波架构,提升供电稳定性。

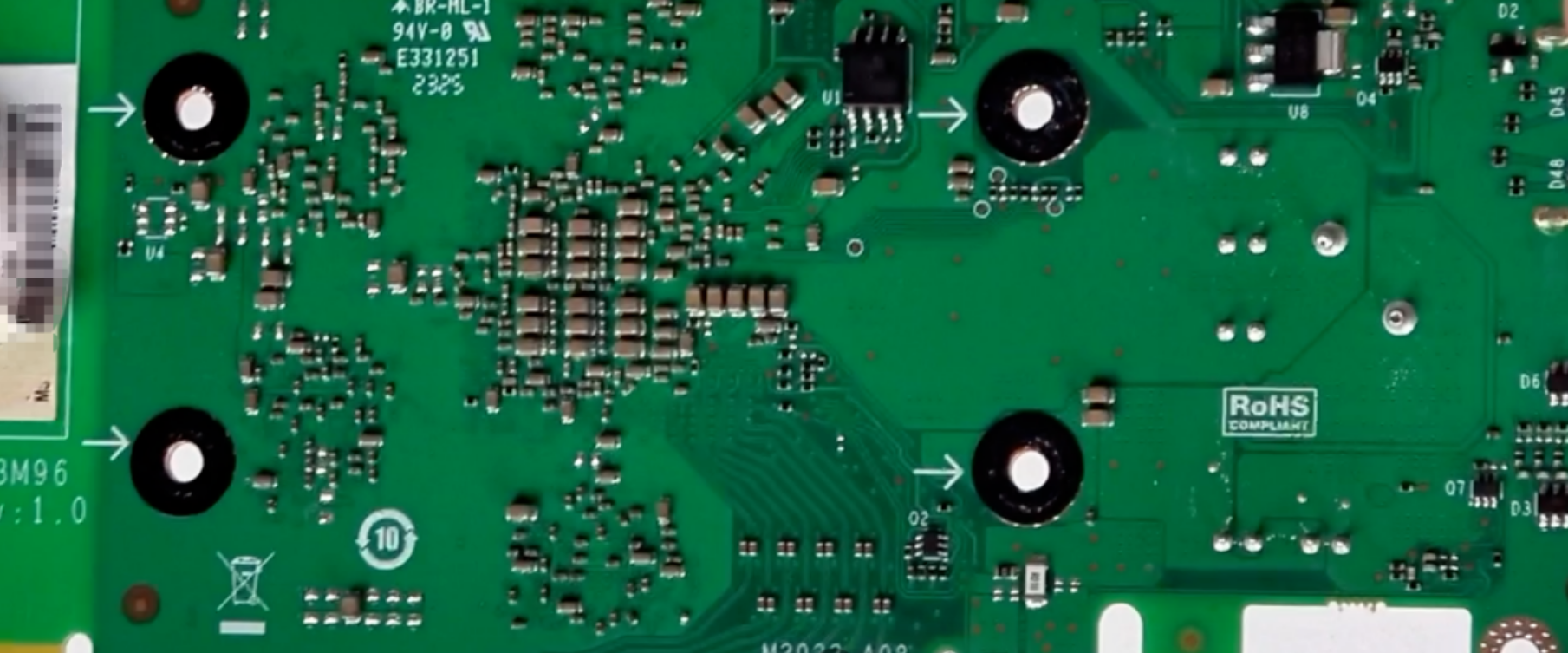

2. 保持电源平面完整性:某消费类产品的传感器板,原设计为4层板,为降低成本改为2层板,且未进行打样验证。设计人员将原电源层用于布设信号线,导致电流环路被切割,电源噪声耦合至信号链路,在暗光环境下出现干扰条纹。此案例表明,并非所有芯片均适用于2层板设计,不同尺寸与形态的电路板设计难度存在差异。硬件工程师需坚持专业判断,充分评估设计可行性,必要时与管理层沟通,避免因盲目执行成本控制要求导致设计失效。

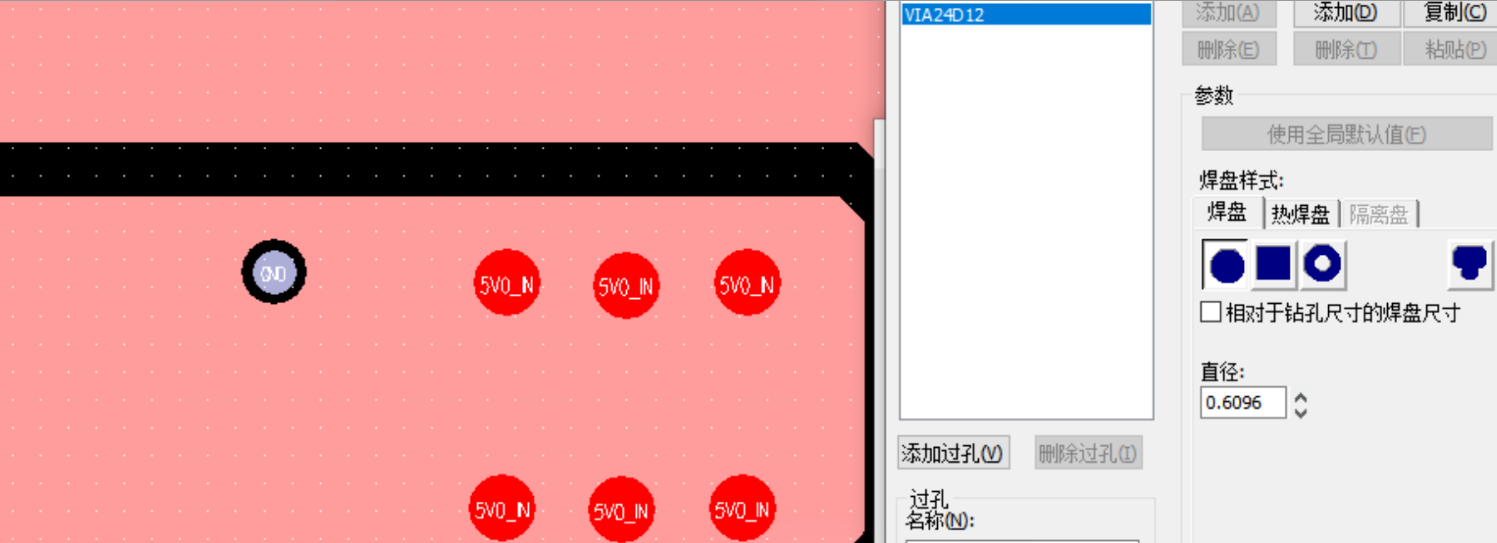

3. 合理设计大电流过孔:某紧急项目中,设计人员为赶工期,深夜完成文件交付板厂,周末审核EQ文件时未发现问题,直至生成BOM时才发现大电流铜皮所用过孔规格过小(0.2/0.4)——经计算,该过孔无法满足3A电流传输需求,且无余量。万幸的是,及时与板厂沟通时,钻孔工序尚未启动,通过调整过孔规格并重新确认EQ文件,避免了批次性报废。

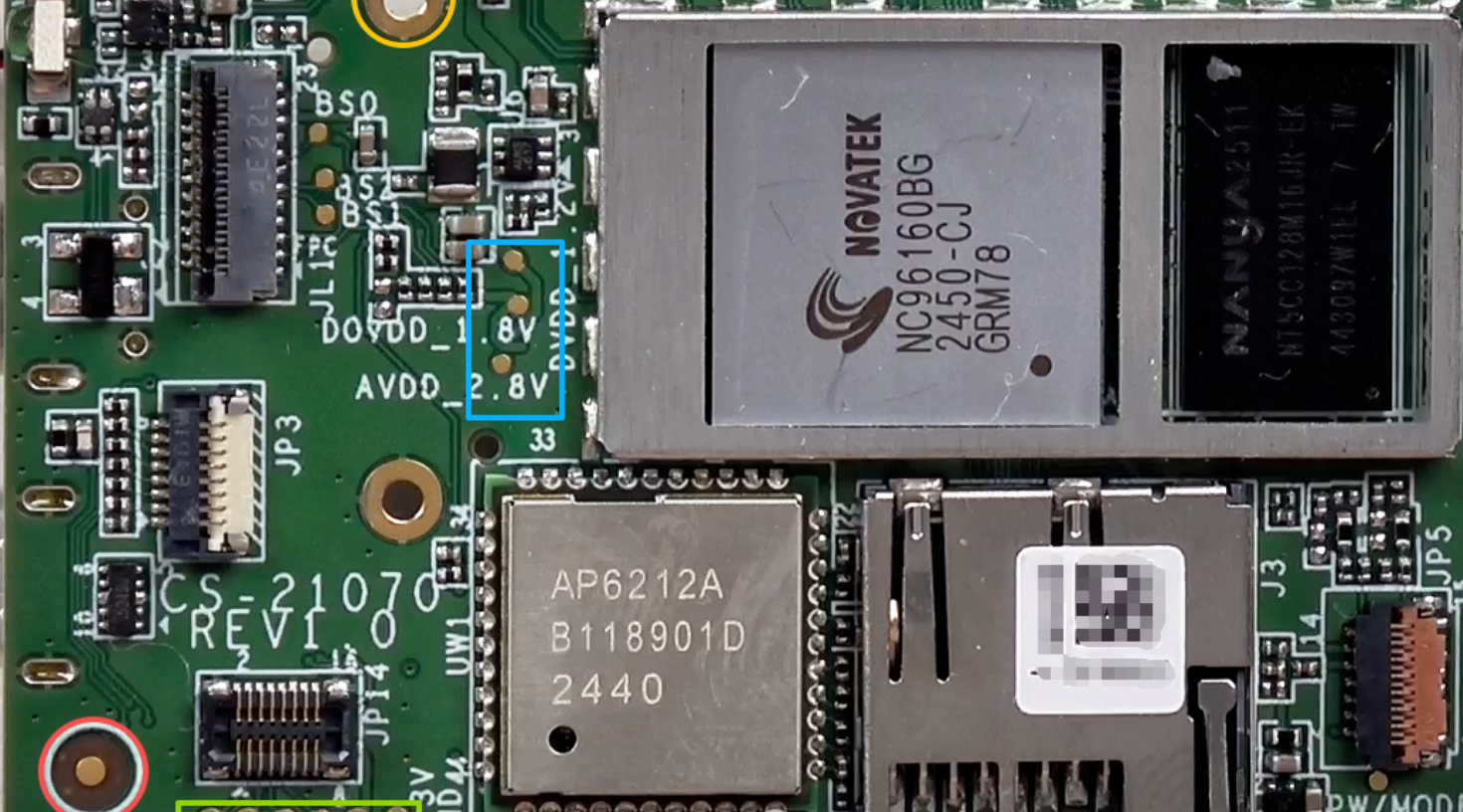

此外,芯片底部需布设通孔接地,若EDA工具中查看不便,可通过CAM、DFM软件进行核验;对于蓝牙、WiFi等射频芯片,若底部未设置接地通孔,将直接导致RF信号调试失败。

EMC实验室测试费用通常为300-800元/小时,若因设计缺陷导致测试失败,不仅增加测试成本,还可能引发管理层对设计能力的质疑。以下为降低EMC风险的实用技巧:

1. 敏感电路增设屏蔽罩:射频、时钟等敏感电路区域,需预留屏蔽罩焊盘(可暂不贴片),通过屏蔽罩减少电磁干扰与辐射。

2. 布设板边地孔阵列:条件允许时,采用3W、20H设计原则,在板边每隔50mil布设一个地孔,形成类似“法拉第笼”的屏蔽结构,提升电磁兼容性。

3. 预留安规器件焊盘:TVS管、ESD防护器件、共模电感等安规器件,即便初期暂不贴片,也需预留焊盘,为后续EMC整改预留空间。

PCB设计若忽视生产工艺要求,将增加SMT贴片难度。虽SMT车间工作人员不会直接指责,但可能影响设计评价与项目推进。以下为符合SMT生产需求的设计要点:

1. 焊盘设计遵循IPC标准:IPC-7351作为封装与焊盘设计的行业标准,严格按照其规定的尺寸设计焊盘,可显著提升SMT焊接良率。

2. 优化丝印清晰度:丝印字符高度不小于1mm,避免覆盖焊盘与测试点;极性标识需与器件本体完全对齐,LED、二极管等有极性器件的方向丝印,应设置在焊盘外部(避免因空间狭小导致标识不清)。

3. 预留MARK点与工艺边:板边需预留至少5mm空白区域作为工艺边,为贴片机夹爪提供夹持空间;同时按要求布设MARK点,保障贴片定位精度。

试产阶段若发现关键信号无法测试,将导致成品装机后出现不良品,增加后续处理成本。

以下为可测试性设计(DFT)的核心要点:

1. 引出关键信号测试点:电源、时钟、复位信号及其他关键链路,需预留直径不小于0.8mm的测试点,便于生产测试与故障排查。

2. 优化BGA封装测试方案:BGA芯片下方的信号若无法直接引出,可通过过孔或盘中孔引至电路板表层,既方便测试,也便于后续返修。

PCB设计属于精细化工种,大量经验源于对过往失误的总结与反思。每批次电路板投板前,建议对照以下 checklist 逐项核验:

-

未使用过的封装库是否完成核验?

-

器件3D模型是否绑定?

-

设计方案是否与结构要求核对一致?

-

高速信号是否完成阻抗控制与等长匹配?

-

电源去耦电容布局是否合理?

-

板边地孔数量是否充足?

-

生产文件是否准确无误?

硬件工程师的核心成就感,往往来源于“一次投板成功”。而上述细节要点,正是实现这一目标的关键基石。若本文对您有所启发,欢迎点赞转发,助力更多硬件设计人员规避弯路。若您在PCB设计过程中也曾踩过坑,欢迎在评论区分享经验——您的实战经历,或许能为他人提供关键的避坑指引。

文章内容参考网络,如侵删。