PCB板蛇形走线:作用、设计要点与常见误区解析

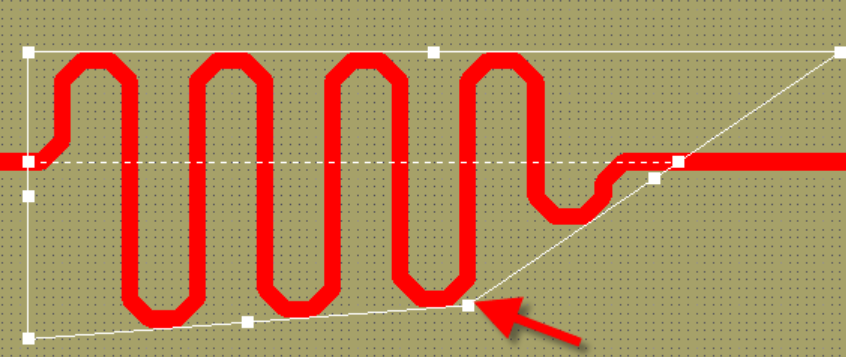

在PCB(印刷电路板)设计中,蛇形走线是一种常见的布线方式,其外形呈连续的“S”形或“Z”形,看似复杂的布局并非为了美观,而是基于高速电路信号完整性、时序控制等核心需求设计的关键布线技巧。尤其是在消费电子、工业控制、通信设备等依赖高速信号传输的产品中,蛇形走线的合理运用直接影响PCB的性能与稳定性。本文将全面解析PCB板蛇形走线的作用、设计要点及常见误区,帮助工程师规避设计风险,提升布线合理性。

一、蛇形走线的核心定义与应用场景

蛇形走线(Serpentine Trace)是PCB布线中通过连续弯折,将信号线设计成类似蛇类爬行轨迹的布线形式,核心特征是可通过调整弯折幅度、间距,精准控制走线总长度。其应用场景主要集中在高速信号传输场景,例如:DDR内存接口、USB 3.0/4.0、PCIe、LVDS差分信号、以太网等,这类场景对信号时序同步、阻抗匹配要求极高;同时也适用于布线空间紧张,需要紧凑排布信号线的PCB设计中。

二、蛇形走线的四大核心作用

蛇形走线的核心价值的是“精准控长”,在此基础上延伸出多重功能,其中等长匹配是其最核心、最常用的作用,其余作用均围绕信号完整性展开。

(一)等长匹配:保证高速信号时序同步

这是蛇形走线最核心的作用。在高速并行信号传输中(如DDR3/DDR4/DDR5内存的地址线、数据线、控制线),多根信号线需要从同一发送端出发,在同一时刻到达接收端,这种要求称为“时序同步”。由于PCB布局限制,不同信号线的直线距离存在差异,部分走线会偏短,此时通过蛇形走线的弯折的方式,人为拉长短线长度,使一组信号线的总长度保持一致,从而确保信号同步到达,避免因时序偏差导致的信号误判、数据丢失。

例如,DDR内存的DQS(数据选通信号)与DQ(数据信号)要求严格等长,偏差需控制在几毫米甚至几十微米以内,蛇形走线便是实现这一要求的最便捷方式。

(二)精准控制信号延迟,匹配时序规范

信号在PCB走线上的传播速度是固定的(约为光速的50%-70%,取决于PCB板材),走线长度直接决定信号传播延迟。在复杂的高速电路中,芯片 datasheet 会明确要求信号延迟范围,蛇形走线可通过微调弯折次数、弯折幅度,精确控制走线长度,进而调整信号延迟,满足芯片的时序规范,避免因延迟过长或过短导致的电路工作异常。

(三)优化信号完整性,减少电磁干扰(EMI)与串扰

合理的蛇形走线设计可在一定程度上优化信号完整性,降低电磁干扰和串扰。一方面,蛇形走线可通过弯折调整线间距,使相邻信号线之间的距离满足“3W原则”(走线宽度的3倍),减少信号线之间的串扰;另一方面,蛇形走线的连续弯折可优化信号回流路径,避免回流电流集中产生强电磁辐射,从而降低EMI(电磁干扰),使PCB满足电磁兼容(EMC)测试要求。

需要注意的是,这种作用是“辅助性”的,若蛇形走线设计不当(如弯折过密、幅度不合理),反而会增加串扰和EMI。

(四)适配紧凑布局,节省PCB空间

在小型化PCB设计中(如手机、智能手表、传感器模块),布线空间极其紧张,部分信号线若采用直线走线,会导致布线冲突或无法连接到目标引脚。此时,蛇形走线可通过紧凑的弯折,在有限空间内完成信号线的连接,实现“短距离内拉长走线”,既解决了布线冲突,又节省了PCB板面积,兼顾了布局紧凑性与信号需求。

三、蛇形走线的关键设计要点

蛇形走线的设计并非随意弯折,需遵循一定规范,否则会适得其反,影响信号质量。以下是核心设计要点,需结合实际PCB需求灵活调整:

(一)控制弯折参数,避免信号畸变

1. 弯折角度:优先采用45°角或圆弧弯折,避免90°直角弯折。90°直角会导致走线阻抗突变,产生信号反射、过冲,影响信号完整性;45°角或圆弧弯折可使阻抗过渡平滑,减少信号畸变。

2. 弯折幅度与间距:弯折幅度(相邻两个弯折之间的距离)不宜过小,建议不小于走线宽度的5倍;蛇形走线的相邻平行段间距需满足3W原则,避免自身串扰(同一根蛇形走线的相邻平行部分产生的干扰)。

3. 走线宽度与厚度:需与其他信号线保持一致,避免因宽度/厚度变化导致阻抗不匹配,影响信号传输。

(二)精准控制等长误差

等长匹配的核心是“误差控制”,不同信号类型的误差要求不同:普通高速信号(如USB 3.0)的等长误差可控制在5mm以内;DDR内存等高频信号的等长误差需控制在1mm以内,甚至更低(如DDR5可要求±0.5mm)。设计时需借助PCB设计软件(如Altium Designer、Cadence)的“等长约束”功能,实时测量走线长度,调整蛇形弯折参数,确保误差在允许范围内。

(三)避免过度弯折,减少寄生参数

蛇形走线的弯折次数不宜过多,过度弯折会增加走线的寄生电容和寄生电感,导致信号延迟增加、带宽降低,甚至产生信号振荡。设计时应遵循“能少弯则少弯”的原则,在满足等长要求的前提下,尽量减少弯折次数,简化蛇形结构。

(四)合理选择布线层

蛇形走线优先布置在信号层,且尽量靠近参考平面(电源层或地层),确保信号有良好的回流路径,减少EMI;避免在PCB边缘、散热片附近布置蛇形走线,防止外部干扰影响信号质量。

四、蛇形走线的常见误区

很多工程师在设计蛇形走线时,容易陷入“盲目弯折”的误区,反而影响PCB性能,以下是最常见的4个误区,需重点规避:

误区1:蛇形走线越复杂,等长效果越好

蛇形走线的核心是“控长”,而非“复杂”。过度复杂的蛇形结构(如密集弯折、多圈缠绕)会增加寄生参数,导致信号畸变,同时增加布线难度和PCB制造成本。只要能满足等长要求,最简单的蛇形结构(如单段“S”形)即可。

误区2:所有信号线都需要蛇形走线

蛇形走线仅适用于高速、并行、对时序同步要求高的信号。低速信号(如GPIO、电源控制线)对时序和阻抗要求较低,无需设计蛇形走线,强行弯折反而会增加信号延迟,毫无意义。

误区3:蛇形走线可以解决所有EMI问题

蛇形走线对EMI的优化是“辅助性”的,无法从根本上解决EMI问题。若PCB布局不合理、线间距过小、回流路径不畅,即使设计蛇形走线,也无法有效降低EMI。EMI的控制核心是布局优化、接地设计,蛇形走线仅作为补充手段。

误区4:等长误差越小越好

等长误差需控制在合理范围,并非越小越好。过度追求极小的误差(如小于0.1mm)会导致蛇形走线过度复杂,增加设计难度和制造成本,且对信号性能的提升有限。应根据芯片 datasheet 的要求,确定合理的误差范围,平衡性能与成本。

五、总结

PCB板蛇形走线的核心作用是通过精准控制走线长度,实现高速信号的时序同步,同时辅助优化信号完整性、适配紧凑布局。其设计的关键在于“合理控长、规范弯折、规避误区”,需结合具体信号类型、PCB布局、芯片要求,灵活调整弯折参数,避免盲目设计。

在实际PCB设计中,蛇形走线并非“万能解决方案”,需结合等长匹配、阻抗控制、EMC设计等多方面因素综合考虑,才能最大化发挥其作用,确保PCB的稳定性和可靠性。对于新手工程师而言,建议先明确信号需求,借助PCB设计软件的约束功能,逐步优化蛇形走线设计,积累实战经验。

文章内容来源网络,仅供学习参考,如侵删。

硬之城集团总部位于中国深圳,服务网络覆盖德国、法国、波兰、新加坡及香港等全球六地,是一家立足中国、辐射全球的电子智造服务商。集团在深圳、江苏、安徽布局自有PCB与PCBA工厂,SMT产线达33条,配备雅马哈全自动贴片线、3D-SPI、3D-AOI、X-ray及BGA返修台等高端设备,拥有超20000㎡生产车间及6000㎡智能仓储。通过自主研发的在线下单平台与智能MES系统,硬之城构建起从设计选型、BOM优化、PCB制版、物料配齐到SMT贴片的全流程数智化交付能力,以项目制管理模式服务全球超2000家新硬件终端。聚焦汽车、工控、储能、AI机器人、医疗、航空航天、网络通讯及安防等高要求领域,依托经验丰富的工程团队与强大的供应链资源,硬之城始终践行“从选型到量产的数智化PCBA一站式服务”,为全球客户提供高品质、快准交付的制造体验,成为新硬件企业值得信赖的在线智能云工厂。

扫码关注硬姐智造PCBA微信公众号